448G/lane标准项目加速落地,共筑智算中心高速传输新基石

随着人工智能大模型技术持续迭代,超节点网络横向扩展与集群规模不断升级,超高速数据传输需求爆发增长,3.2Tb/s高阶接口标准落地已迫在眉睫。面向后224G/lane时代的算力互联演进需求,开放数据中心委员会(ODCC)448G焦点组,启动448G/lane标准项目研制工作。其聚焦补齐下一代448G高速互联技术空白,统筹制定统一的物理层规范,构建光电接口协议与标准化测试体系,加速AI智算中心高速互联技术规范统一,推动新一代高速互联方案的技术成熟、产业落地与规模化部署,为大规模AI集群高效协同、异构算力高速传输筑牢底座支撑。

一、需求爆发:

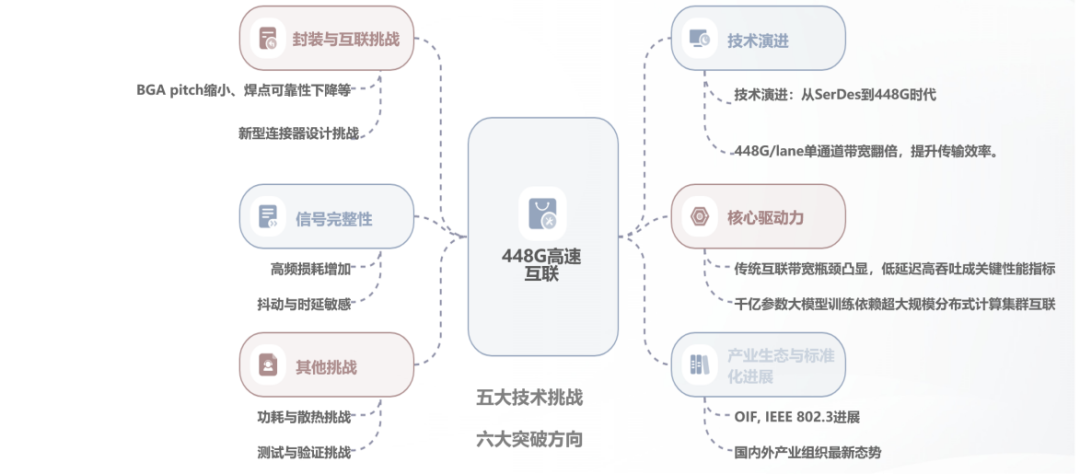

AI算力爆发催生高速互联新需求

当前,千亿参数级大模型训练与超大规模分布式计算集群互联,对算力中心互联技术的带宽、延迟与吞吐性能提出了较高要求。传统224G/lane互联技术无法支撑3.2T接口速率的演进需求。448G/lane单通道的带宽较224G/lane实现翻倍,成为突破智算中心带宽瓶颈、承接下一代AI算力集群互联的关键技术。ODCC已在2025年11月率先发布《448G/lane高速互联需求白皮书》,系统梳理技术挑战与发展路径,为本项目奠定了产业共识基础。

图 1 448G高速互联需求

二、多方协同:

构建国际开放标准生态

448G/lane标准项目是ODCC推动国内算力基础设施与国际标准接轨的重要实践。项目采用全球化协同研发模式,计划深度联动国内外相关标准组织成立448G/lane标准工作组,实现技术标准与国际接轨的同步创新。目前,项目组汇聚了腾讯、美团、博通(Broadcom)、是德科技(Keysight)、立讯、TE、华为、中国信通院等全球30余家头部企事业单位的技术专家,覆盖用户需求、器件材料、芯片设计、模块制造、测试验证、设备研发等全产业链环节,形成“产学研用”一体化的标准制定协作体系。

三、核心技术:

三大维度破解下一代互联技术难题

项目围绕三大核心技术展开,系统性解决AI智算中心高速互联的关键问题。

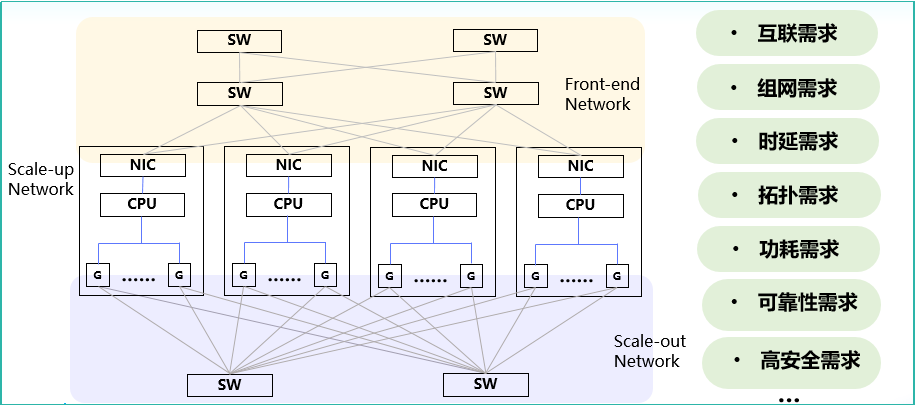

1. 下一代智算DC网络需求与方案选型

互联与组网需求:面向Scale-up与Scale-out两级网络架构,梳理AI集群的多维度互联拓扑与组网模型;

关键性能指标:针对时延、拓扑、功耗、可靠性、安全性等核心指标,明确448G速率下的量化需求与设计边界,为后续技术方案选型提供依据。

图 2 下一代智算 DC 网络需求与方案选型

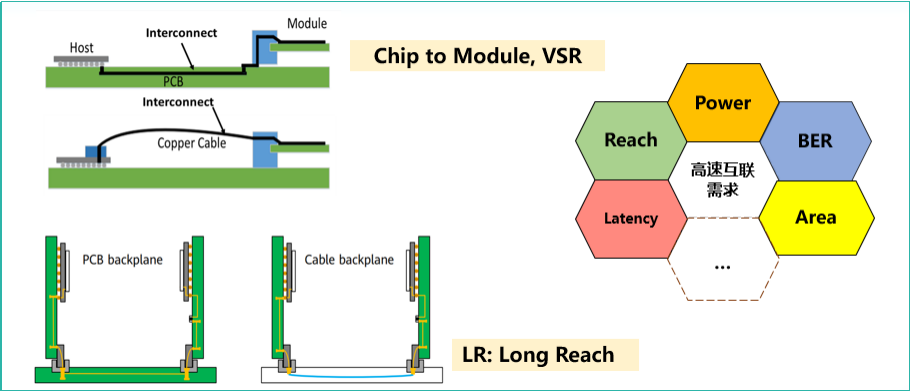

2. 下一代高速互联场景、需求与挑战

短距场景:聚焦芯片到模块的PCB、铜缆互联链路,解决高频信号传输的损耗与抖动问题;

长距场景:针对PCB背板、线缆背板等跨设备互联场景,重点优化传输距离、功耗、误码率与面积成本之间的平衡;

多维度技术挑战:围绕传输距离、功耗、时延、误码率、硬件面积等核心指标,建立多目标优化的技术评估体系。

图 3 下一代高速互联场景、需求与挑战

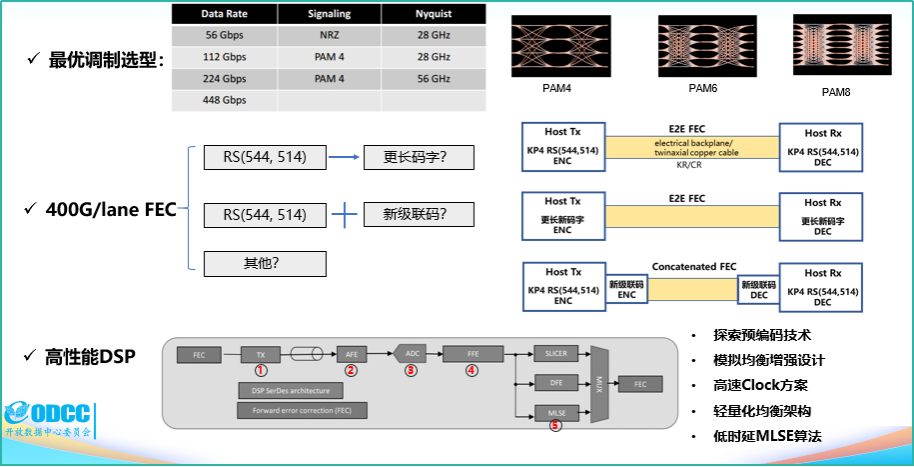

3. 下一代调制、FEC、DSP等关键技术选型

最优调制选型:对比PAM4、PAM6、PAM8等调制格式,明确448Gbps速率下的Nyquist频率与信号完整性表现,确定最优调制及对应的无源链路方案;

FEC技术演进:基于RS(544.514)等现有方案,探索更长码字、新级联码等FEC增强路径,对比端到端FEC与级联FEC架构的性能差异;

高性能DSP设计:围绕预编码、模拟均衡、高速时钟、轻量化均衡架构、低时延MLSE算法等方向,优化DSP处理流程,降低448G速率下的信号处理开销与时延。

图 4 下一代调制、FEC、DSP等关键技术选型

四、核心目标:

全链路规范制定,加速技术规模化落地

为加快高速互联技术成熟迭代与规模化落地应用,进一步夯实智算集群、算力中心互联等场景的基础设施能力,项目围绕技术突破、测试体系与产业协同三大核心方向统筹推进工作,为算力网络全域贯通、智算基础设施高质量发展筑牢高速传输底座,引领下一代算力中心高速互联技术的演进与产业化进程。

统一技术规范:制定覆盖物理层架构、电气接口、光接口的全链路技术标准,明确调制格式、FEC方案、连接器设计等关键参数,解决高频损耗、抖动与时延敏感等技术痛点;

完善测试体系:建立适配448G/lane速率的测试验证规范,覆盖芯片、模块、系统全层级测试,为产业界提供可落地的测试参考依据;

推动产业落地:联合产业链企业开展原型验证与联调测试,加速448G/lane技术从标准规范向产品化、规模化应用转化,支撑超大规模智算集群的高效互联。

作者

高 威 gaowei1@caict.ac.cn

徐 丽 innon.xu@huawei.com

审核

王少鹏 wangshaopeng@caict.ac.cn