智算互联芯粒实验室正式成立,携手产业共促智算芯粒互联全栈测试与标准建设

近日,ODCC春季全体会议在浙江舟山成功召开。会上,ODCC新测组组长郭亮,ODCC网络工作组组长、腾讯基础网络中心总监何泽坤,奇异摩尔联合创始人、产品解决方案副总裁祝俊东,博通网络架构总监何宗应,江波龙企业产品市场总经理刘洋共同完成“智算互联芯粒实验室”(ACCL – AI Connectivity Chiplet Lab)成立仪式。

智算互联芯粒实验室由中国信通院和腾讯牵头,联合奇异摩尔、博通等产业链上下游企业共同发起,旨在汇聚产学研核心力量,聚焦芯粒技术与智算互联的深度融合,攻克智算产业发展中的互联瓶颈,补齐国产智算芯粒短板,助力我国智算产业高质量发展。

ACCL实验室聚焦智算场景下芯粒互联的开放标准与工程化落地,将围绕“技术研发—标准制定—测试验证—产业协同”四位一体路径,打通从XPU片间互联、统一内存池到整集群系统的全栈技术链条,全面支撑节点内Scale-Up的多样化智算场景需求。

首期聚焦ETH-X协议

构建互联芯粒验证平台

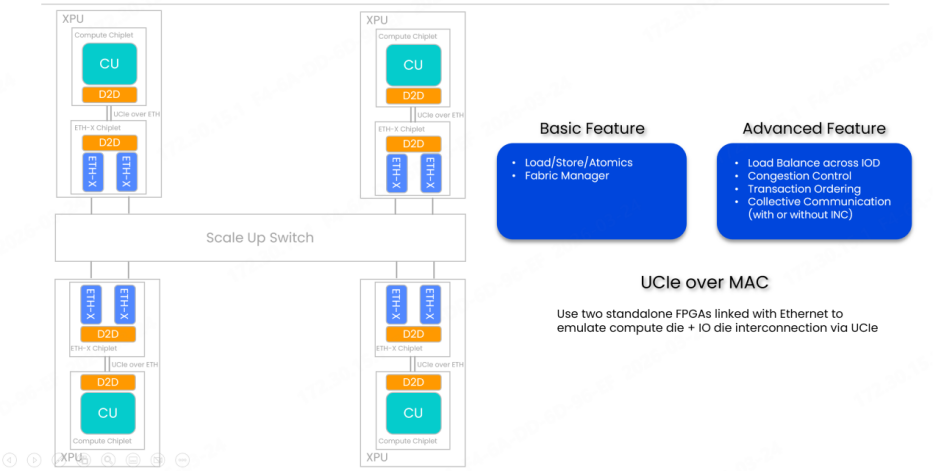

实验室首阶段将基于ETH-X Scale-Up互联协议,联合XPU厂商、交换机厂商等生态伙伴,搭建更接近于XPU真实部署线速性能的ETH-X协议硅前验证平台。该平台采用Altera FPGA板卡构建小规模集群,并创新性地采用“UCIe over MAC”技术,用两片FPGA分别模拟计算芯粒与IO芯粒,真实还原跨芯粒数据高效传输过程,为硅前验证提供接近线速的测试环境。

图1 XPU with ETH-X Chiplet

芯粒验证平台将聚焦于以下Scale Up互联实现中的核心技术领域:

1. 计算芯粒将流量在多个IO芯粒间进行路径状态感知负载均衡;

2. XPU根据网络拥塞状态自适应调整业务发送;

3. 集群内XPU的集合通信机制(包括交换机在网计算);

4. 探索XPU通信的有效事务序保证机制。

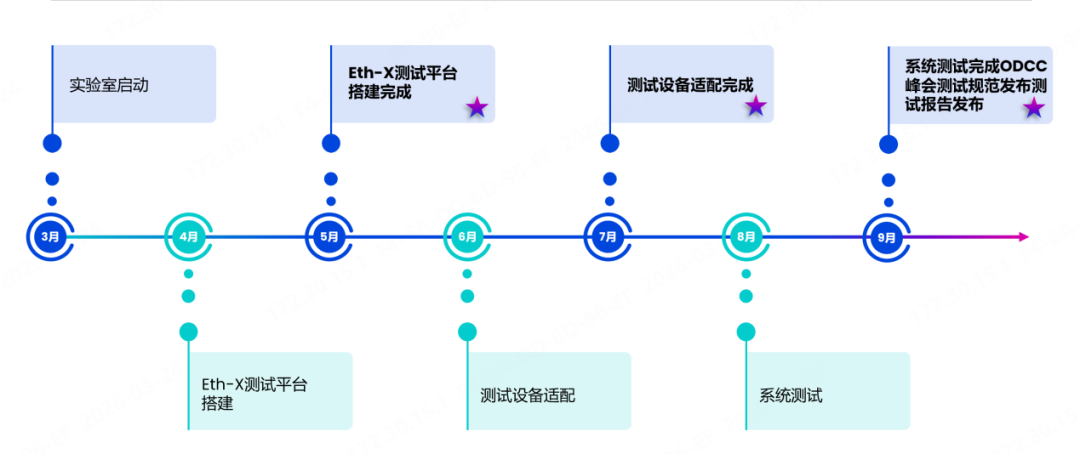

实验室成果发布计划

图2 成果发布计划

实验室技术前瞻:

面向统一内存池的下一代互联架构

随着Agent场景中多轮调用、长上下文与工具链的普及,KV Cache的显存占用被显著放大。在大模型推理过程中,prefill阶段偏重计算,而decode阶段对内存与延迟高度敏感,若二者争抢有限的片上或卡上显存,将引发首Token时延升高、XPU利用率下滑及跨节点数据搬运开销激增等问题。实验室将探索以IO芯粒作为协议调度枢纽,构建无阻塞、低延迟的统一内存池架构,实现GPU/HBM与系统内存之间的高效协同。通过物理解耦与动态按需分配,实现计算与内存资源的弹性伸缩,有效提升系统吞吐并收敛长尾延迟,为下一代AI推理提供关键支撑。

面对大模型的持续演进,IO芯粒凭借其卓越的灵活性与可扩展性,已成为智算底座的关键技术。未来,ACCL实验室将秉持开放共赢理念,联合产业链上下游,以IO芯粒为协议调度枢纽,围绕XPU、统一内存池和CPU等异构单元,开展片间互联标准制定与原型测试验证,加快统一内存访问架构在智算场景落地,降低跨芯粒交互延迟,共建更解耦、更高效的智能计算基础设施。

联系人

孙老师 15732071244 suncong@caict.ac.cn

王老师 13701380040 wangshaopeng@caict.ac.cn

ODCC秘书处联系人

刘老师:13488889649 邮箱:liupengyun@caict.ac.cn