ODCC | 面向高带宽域的Scale-up算力高速互联技术

随着人工智能模型参数规模持续突破万亿级,训练任务对算力密度与通信效率的要求迈入全新量级。在大规模分布式训练场景中,模型并行、张量并行与混合专家(MoE)架构的规模化落地,使得GPU节点间的通信流量呈指数级增长。传统跨节点通信架构因带宽受限、时延较高,频繁引发“GPU空转”现象——即计算单元因等待数据传输而处于闲置状态,严重制约整体训练吞吐与资源利用率。

为突破这一瓶颈,业界逐步转向“超节点”架构,即在单个服务器节点内集成更多GPU卡,通过提升机内互联带宽、降低通信跳数,从根本上减少跨机通信压力,旨在于构建一个高带宽、低时延、可扩展的本地互联域(Scale-Up Domain),实现GPU间高效协同。

GPU机内高速互联的关键技术需求

为支撑万亿参数模型的高效训练,机内高速互联需满足以下三大核心需求:

1.高密度GPU扩展能力

传统PCIe点对点互联架构受限于拓扑结构与信号完整性,通常仅支持单节点8卡互联。面向未来超大规模模型训练对算力的需求,亟需突破这一限制,实现单节点16卡、32卡甚至更高密度的GPU直连,构建统一的高带宽通信域。

2.T比特级聚合带宽

在张量并行场景下,单次前向/反向传播需在多个GPU间同步海量梯度与激活值,对互联链路的聚合带宽提出Tbps量级要求。传统接口(如PCIe Gen5)已难以满足,需采用更高物理层速率的新型互连方案。

3.亚微秒级通信时延

训练效率高度依赖通信延迟。任何额外的协议开销、排队延迟或重传机制都会放大GPU空闲时间。因此,互联架构需在协议栈层面精简冗余层,优化传输路径,并通过硬件级加速实现端到端亚微秒级响应。

高速互联架构的创新路径

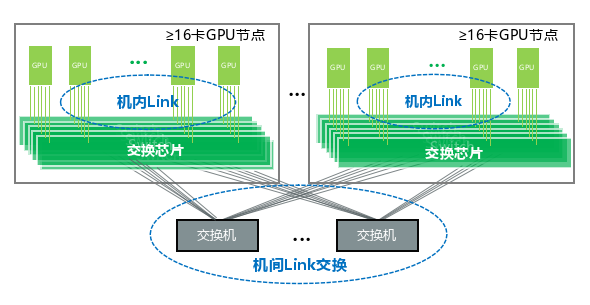

图1 智算高速互联Link总线方案

当前,新一代互联架构正朝着“融合式总线+智能交换”的方向演进,如图1所示。该架构摒弃传统分层网络模型,采用统一的低延迟通信协议,实现机内与机间互联的无缝衔接。其关键技术特征如下:

1 物理层优化

采用差分信号传输、轻量级前向纠错(FEC)编码与高密度布线技术,在保障信号完整性的同时,实现单通道200Gbps以上的传输速率,有效降低物理层延迟与误码率。

2 链路层可靠性增强

引入基于信用的流控机制(Credit-Based Flow Control),动态感知网络拥塞状态,避免数据包丢失与缓冲区溢出;结合循环冗余校验(CRC)与链路级重传机制,确保在高并发场景下实现无损通信。

3 统一内存寻址与语义支持

通过虚拟地址空间共享机制,使集群内所有GPU可直接访问彼此显存,无需显示数据拷贝。同时,支持内存语义操作(如Read/Write/Atomic),允许网络设备直接参与内存数据的读写与规约,显著降低CPU/GPU负担,提升异构计算效率。

4 开放架构与生态兼容

系统设计遵循开放接口标准,支持多厂商算力芯片、存储单元的即插即用。底层通信协议兼容主流以太网物理层生态,可复用成熟光模块、光纤布线与运维工具,降低部署与维护成本。

当前国内主流的Scale-Up互联技术,例如ETH-X、EthLink、OISA、OLink、CLink等,基本都在沿着该创新路径持续演进,而中兴通讯的无线缆正交互联架构超节点,可兼容适配国内主流Scale-Up互联技术,助力推动Scale-Up互联生态的健康发展。

高性能互联网络的演进方向

未来,高速互联架构将将聚焦在网计算、光互联集成两大核心维度展开技术演进。

1 在网计算(In-Network Computing)

将深度学习训练中高频使用的AllReduce、AllGather等集合通信操作,下沉至网络交换节点执行。交换设备在接收数据后直接完成梯度聚合、均值计算等操作,大幅减少主机间数据搬运量,释放计算资源,提升整体系统吞吐。

2 光互联集成

随着硅光、CPO(Co-Packaged Optics)等光电子技术的成熟,高速互联将逐步由电互连向光电混合甚至全光互联演进。这将带来更高的带宽密度、更低的功耗与更远的传输距离,为下一代超大规模智算集群提供物理层基础支撑。

在AI大模型训练进入“算力+通信”双驱动时代,构建高效、可扩展、低延迟的Scale-Up互联体系,已成为突破训练瓶颈的关键路径。通过融合先进物理层设计、智能流控机制与内存语义协同,新一代互联架构正从“连接设备”迈向“协同计算”,为构建自主可控、高效节能的智能算力基础设施提供坚实支撑。

联系人

信通院 王老师 13701380040

信通院 孙老师 15732071244

中兴通讯 杨老师 13813897434

ODCC秘书处联系人

刘老师:13488889649 邮箱:liupengyun@caict.ac.cn